TOPPAN Develops Coreless Organic Interposer for Next-Generation Semiconductors—World’s First Supporting Standalone Electrical Inspection

Press release from the issuing company

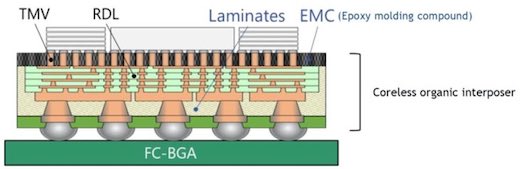

Illustration of cross-sectional structure of coreless organic interposer

©TOPPAN Inc.

Contributing to significant reduction in loss from chip disposal caused by interposer defects

Tokyo – TOPPAN Inc. (TOPPAN), a TOPPAN Group company and wholly owned subsidiary of TOPPAN Holdings Inc., has addressed a challenge for heterogeneous integration of semiconductors by developing a high-reliability coreless organic interposer1 for next-generation semiconductors.

With this new coreless organic interposer, TOPPAN has used a material with a low coefficient of thermal expansion (CTE) to reinforce both sides of the redistribution layer (RDL). While supporting fine pitch interconnections and a low CTE, the simple coreless structure also adds rigidity. This means that the organic interposer itself can be independent from the carrier, delivering the world’s first organic interposer for which standalone electrical inspection assurance is possible. Reliability is enhanced, making it possible to contribute to a significant reduction in loss due to chip disposal resulting from interposer defects.

The new coreless organic interposer will be showcased in the TOPPAN booth at JPCA Show 2024, which will be held at the Tokyo Big Sight international exhibition center from June 12 to 14.

Background

Heterogeneous integration, in which multiple different types of chips are integrated on an interposer, is widely used to enhance semiconductor performance. Silicon interposers are currently the predominant type, but due to cost considerations, growth in semiconductor packaging adopting organic interposers is expected in the future. However, general organic interposers have poor structural rigidity, and standalone handling is difficult. This mean that they need to be fixed to a carrier or the like for electrical inspection, and the inability to confirm conduction on both the front and rear sides in such a state has presented a challenge.

TOPPAN’s new coreless organic interposer for next-generation semiconductors has both sides of the RDL reinforced with a low CTE material. The simple coreless structure supports fine pitch interconnections and a low CTE as well as adding rigidity. This makes it possible for the organic interposer to be independent of a carrier, facilitating standalone electrical inspection assurance of the organic interposer.

If an organic interposer is defective, the LSI chip onto which it is mounted also has to be disposed of. However, if the organic interposer has high-reliability and is subject to electrical inspection assurance in advance, it will be possible to significantly reduce loss due to disposal of chips.

Product features

1) Separating the interposer from the carrier during the manufacturing process makes standalone electrical inspection assurance possible, enhancing reliability and enabling supply as a known-good substrate.

2) The CTE is approximately 45% lower than conventional packaging substrates, making it possible to prevent cracks that arise due to differences between the CTEs of FC-BGA substrates and RDLs.

3) The narrow pitch mold resin through-mold via (TMV) structure enables fine routing/fine interconnection with a minimum connection terminal pitch of 40μm (conventionally 130μm) on the chip side and 130μm (conventionally 300μm) on the substrate side.

4) Due to the scalability of panel level manufacturing, large sizes of more than 100 mm sq. can be supported.

Future

TOPPAN is aiming for its new product to be adopted for organic interposers and semiconductor packaging substrates for applications such as data center CPUs and AI accelerators. Samples of next-generation semiconductor-packaging-related products including the new structure will be available from fiscal 2027, with the launch of mass production scheduled for fiscal 2028.

1. An interposer is a substrate used for electrically connecting front and rear circuits with through-mold vias.

About JPCA Show 2024

• Dates & times: June 12 to 14, 2024 10:00—17:00

• Venue: Tokyo Big Sight, East Hall

• *TOPPAN will participate in JPCA Show 2024 (East Hall 3/booth 3A-28)

• Organizers: Japan Electronics Packaging and Circuits Association, Japan Institute of Electronics Packaging, Japan Robot Association

Official website: https://www.jpcashow.com/show2024/en/exhibition/index.html

- Questions to ask about inkjet for corrugated packaging

- Can Chinese OEMs challenge Western manufacturers?

- The #1 Question When Selling Inkjet

- Integrator perspective on Konica Minolta printheads

- Surfing the Waves of Inkjet

- Kyocera Nixka talks inkjet integration trends

- B2B Customer Tours

- Keeping Inkjet Tickled Pink

© 2024 WhatTheyThink. All Rights Reserved.

Discussion

Only verified members can comment.